新製品情報

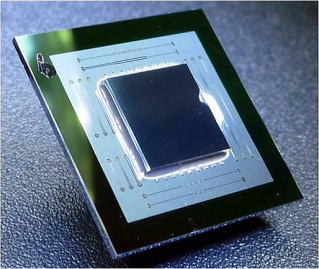

■SiP(シリコンインターポーザ)による3次元実装

| 近年の技術高度化に伴い高密度実装のニーズが高まっており、各社ともに実装面積の削減に向け努力をされていると思います。 そのような技術的課題へのソリューションとして、当社はSIP(シリコンインターポーザ)による3次元実装技術を保有しております。 当社製の3次元実装ソフト(STEERSIP)を使用し、SIPの設計だけではなく、各種解析(応力解析、電磁界解析、熱解析など)を一貫してサポート致します。 お問い合せはこちら |

|

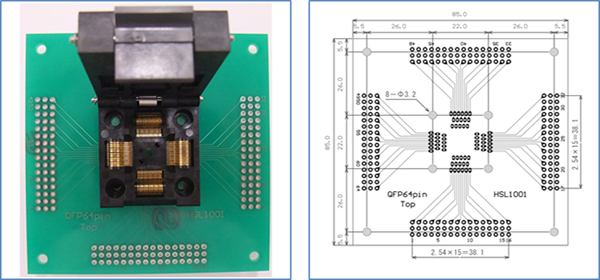

■QFP評価基板

【概要】

基板中央に実装されたソケットのランドから配線が引き出され、周囲のTPラ

ンドに1対1で接続されています。

【主な仕様】

・基板寸法 85.0×85.0×1.2mm(W×H×T)

・基板材質 FR-4

・表面処理 はんだレベラー

・TPランド形状 2.54mmピッチ、穴径Φ1.0mmTH

・ソケット 0.5mmピッチQFP64ピン用クラムシェル

(2type) 0.5mmピッチQFP100ピン用クラムシェル

ソケット搭載済み

お問い合せはこちら

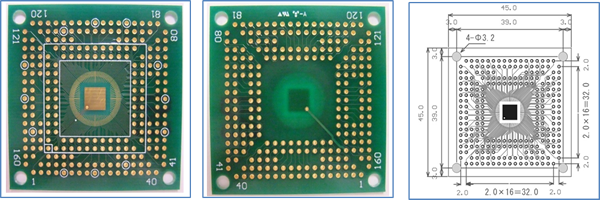

■ワイヤボンダー評価基板(ベアチップ評価)

【概要】

基板中央にICをダイボンディングし周辺ランドにワイヤーボンディングします。

また基板中央にはIC裏面パッド接続ランドも設けてあります。

基板周囲にはTPランドを配置し、基板偶数ピンについてはパターンカットによ

り接続パターンを短くできるようになっております。

また、当社にてワイヤーボンディング加工も承っております。

【主な仕様】

・基板寸法 45.0×45.0×1.0mm(W×H×T)

・基板材質 FR-4

・表面処理 Auボンディングメッキ(Ni3~5µm、Au0.3µm以上)

・TPランド形状 2.0mmピッチ、穴径Φ0.8mmTH

・その他 ベアチップ裏面接続可

お問い合せはこちら

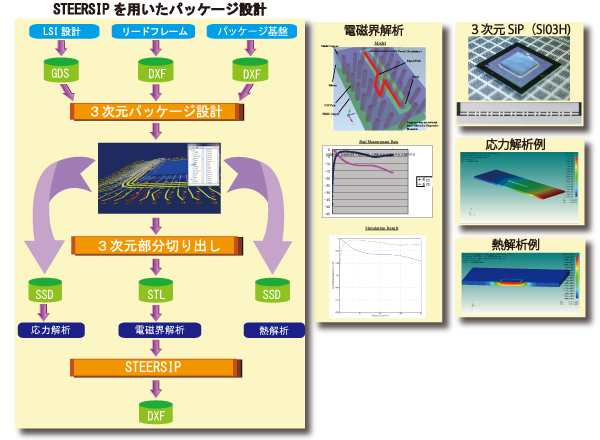

■STEERSIPによる3次元パッケージ設計

・ LSIデータ及びパッケージデータを統合したデータベースを採用

・ 複数のLSIを積層したバッケージの設計・懸賞

・ ボンディングワイヤー等の配線設計及び3次元DRC

・ 各種シミュレーションインターフェース(応力解析、電磁界解析、熱解析)