Information on new products

■3-D implementation by SiP (silicon interposer)

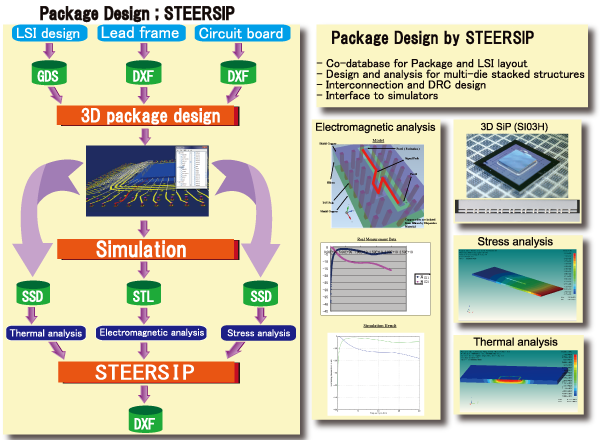

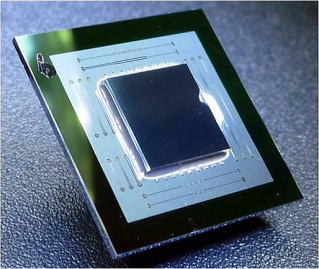

| We think the needs of high-density packaging is increasing due to the advanced technology in recent years, and companies have been efforts towards the reducing of the mounting area. As a solution to the technical problem such, the Company holds a three-dimensional packaging technology by SIP (silicon interposer). Using three-dimensional implementation of our software (STEERSIP), we will consistently support the design of the SIP, stress analysis, electromagnetic field analysis, and thermal analysis. Contact Us is here. |

|

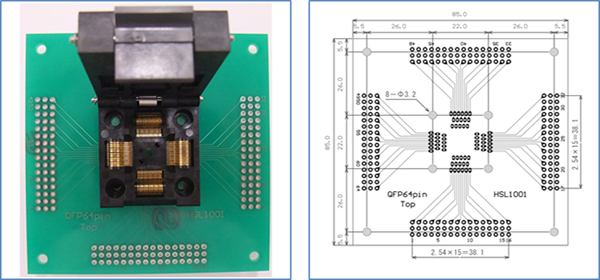

■QFP evaluation board

【Overview】

Wiring is pulled out from the land of the socket mounted on the substrate center, and is connected to the TP surrounding land on a one-to-one.

【Overview】

・Substrate dimensions 85.0×85.0×1.2mm(W×H×T)

・Substrate material FR-4

・Surface treatment Solder leveler

・TP land shape 2.54mm pitch , hole diameterΦ1.0mmTH

・Socket 0.5mm pitch QFP64pin用Clam shell

(2type) 0.5mm pitch QFP100pin用Clam shell

Socket mounted

Contact Us is here.

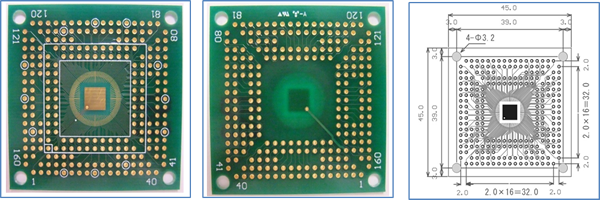

■Wire bonder evaluation board (bare chip evaluation)

【Overview】

The die-bonded to the substrate center IC, and then wire bonded to the surrounding land. And, the back pad of the IC can also be connected to the center of the substrate.

Place the TP land around the board, the board even pin is able to shorten the connection pattern by pattern cut.

In addition, we have also heard of the wire bonding process.

【Overview】

・Substrate dimensions 45.0×45.0×1.0mm(W×H×T)

・Substrate material FR-4

・Surface treatment Au Bonding plating(Ni3~5µm、Au0.3µm以上)

・TP land shape 2.0mm pitch ,hole diameterΦ0.8mmTH

・Socket Can be connected to the back of the bare chip

Contact Us is here.

■Three-dimensional package design according to STEERSIP

・ We employ a database that integrates data package and LSI data.

・ Design and Verification of the package to accumulate some LSI.

・ 3-D DRC(Design Rule Check) and wiring design such as a bonding wire.

・ Various simulation interface (Stress analysis, electromagnetic field analysis, thermal analysis)